The Product

See it in action.

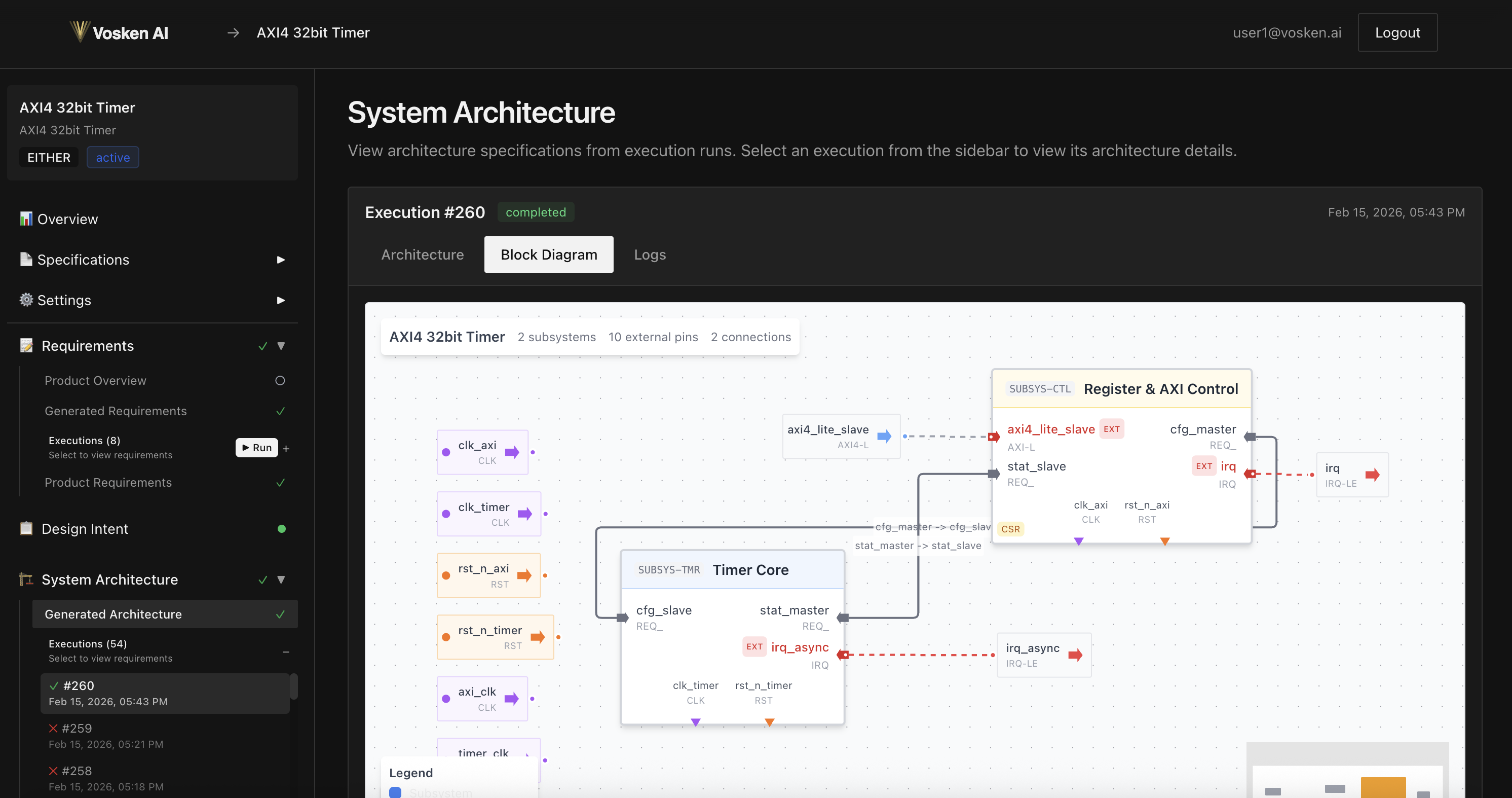

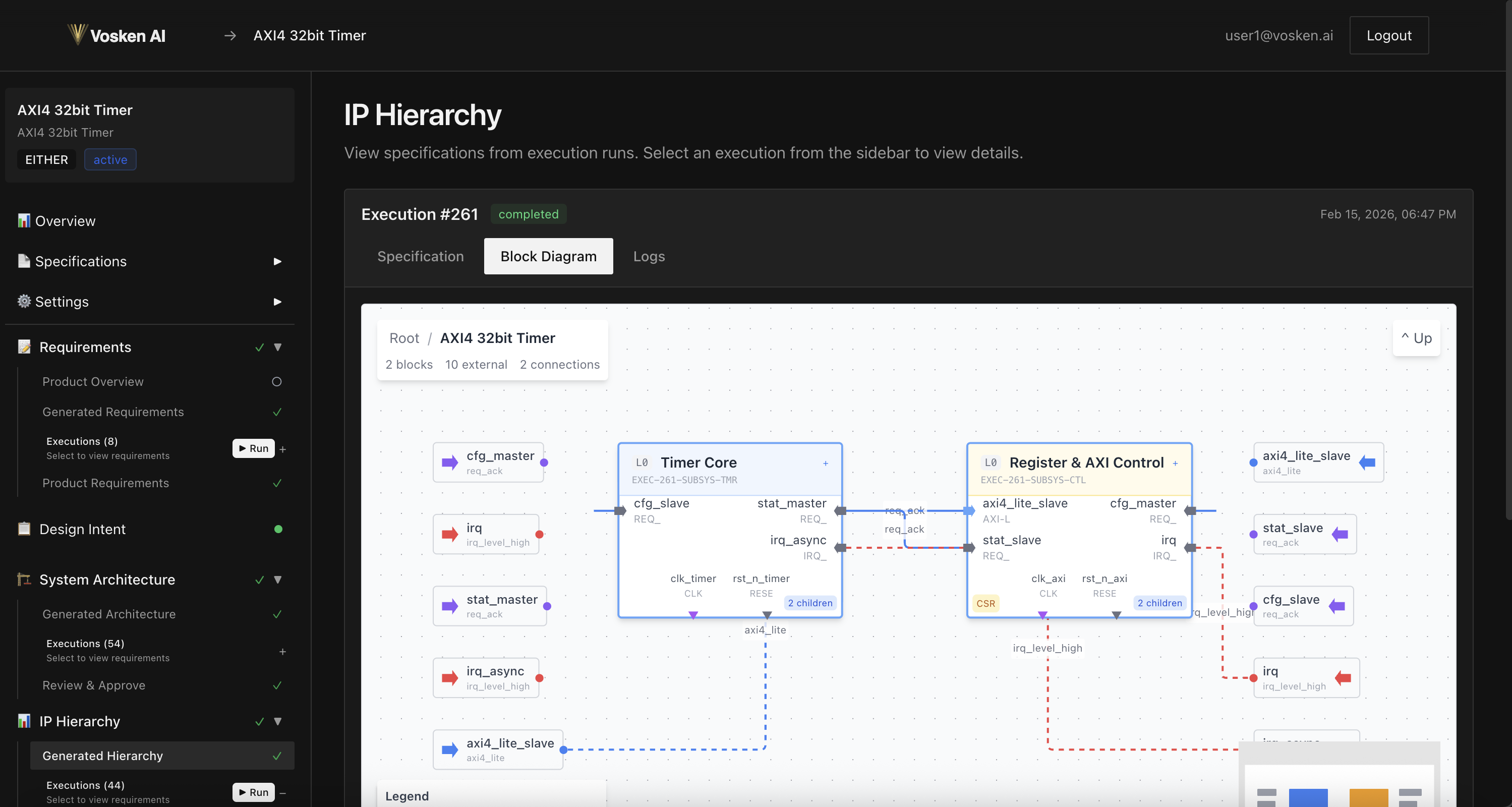

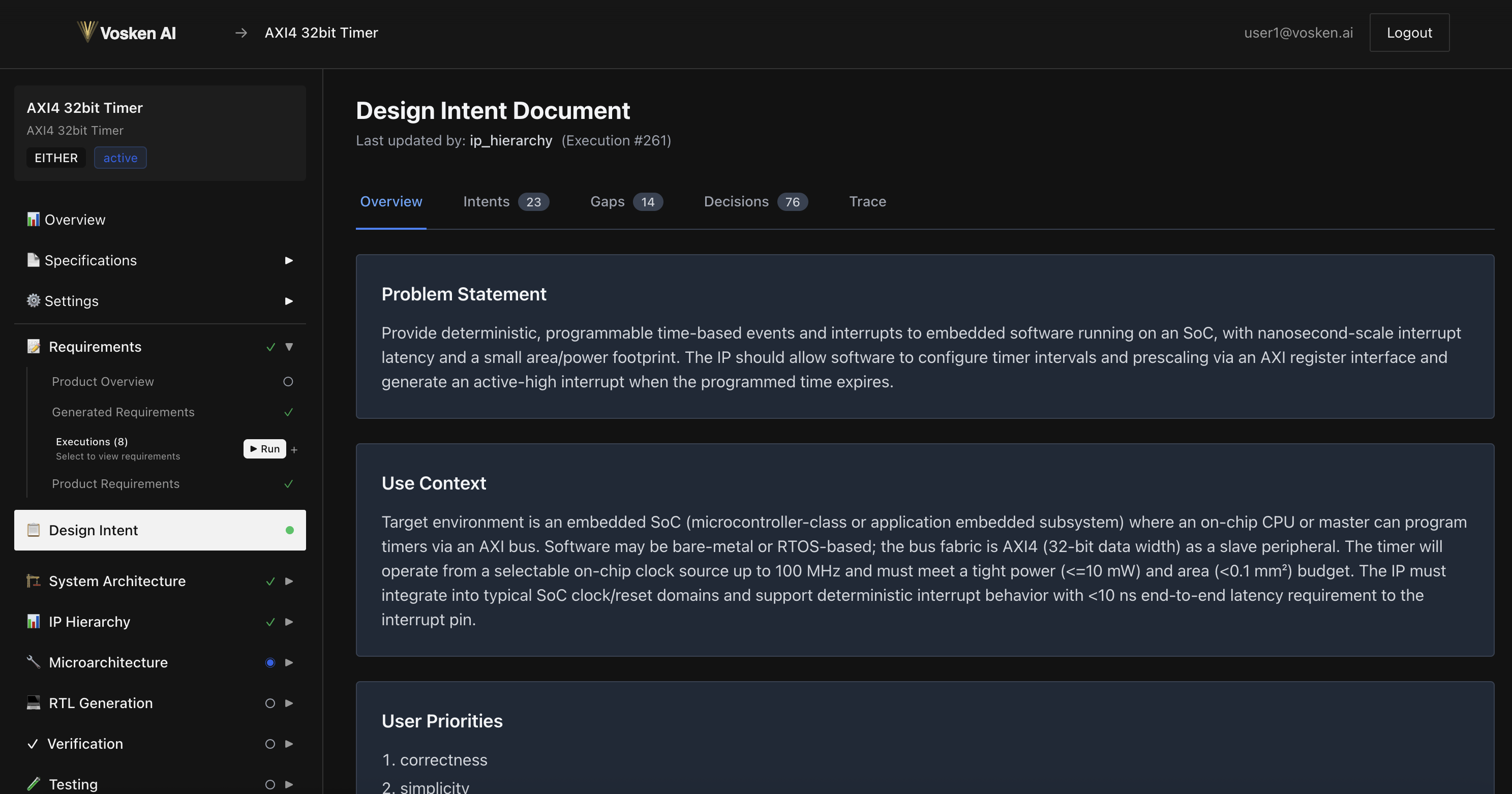

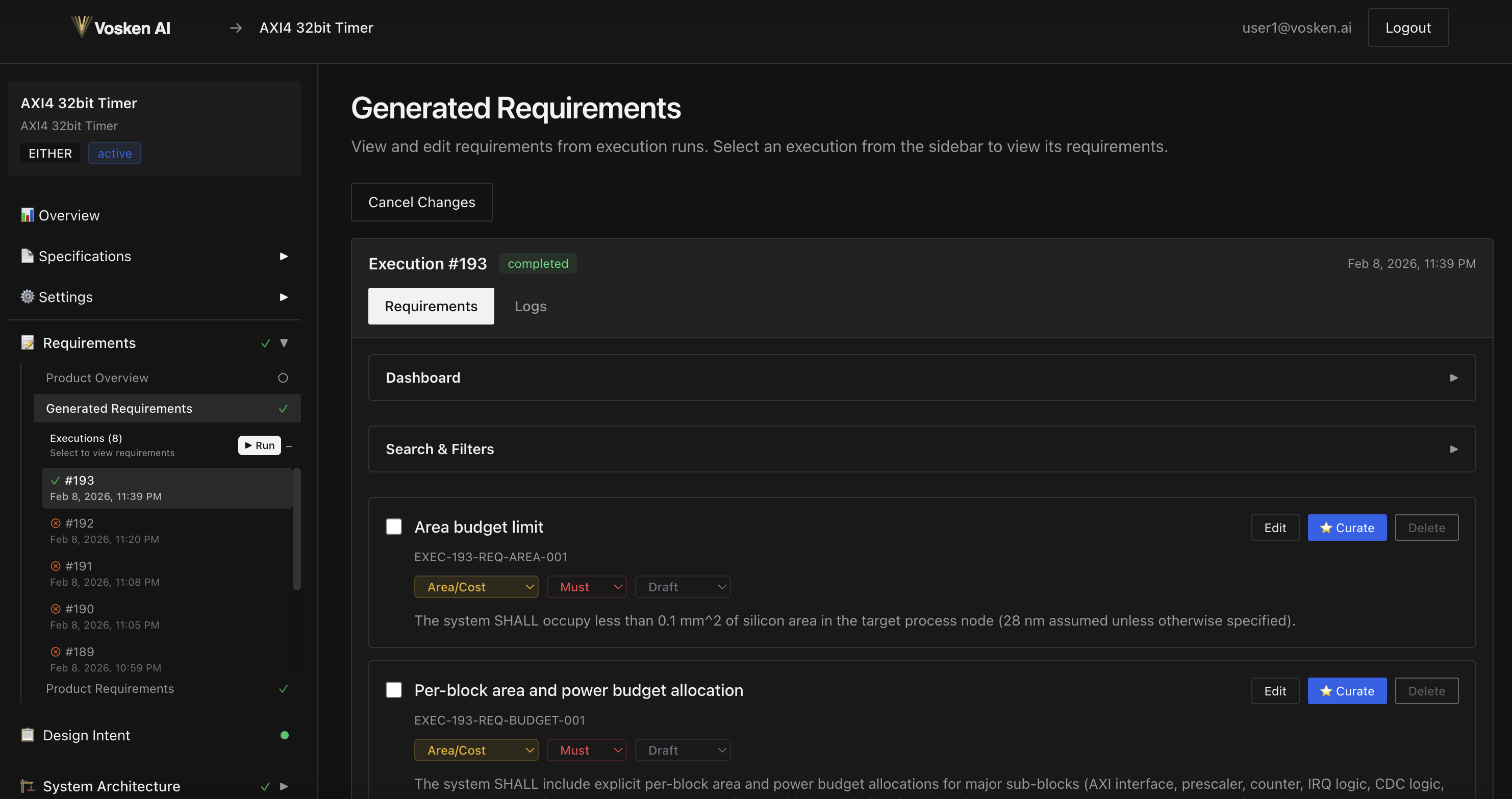

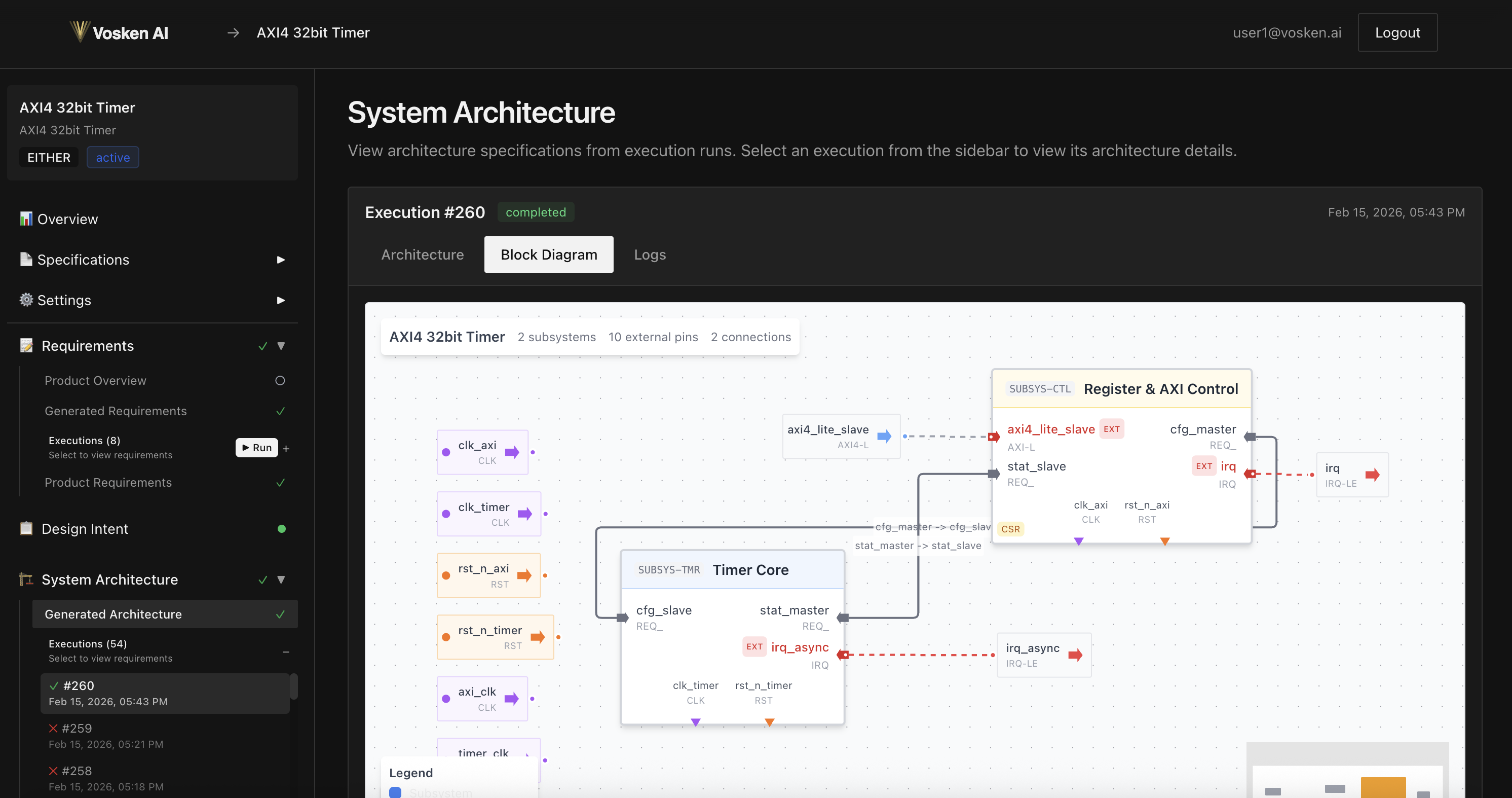

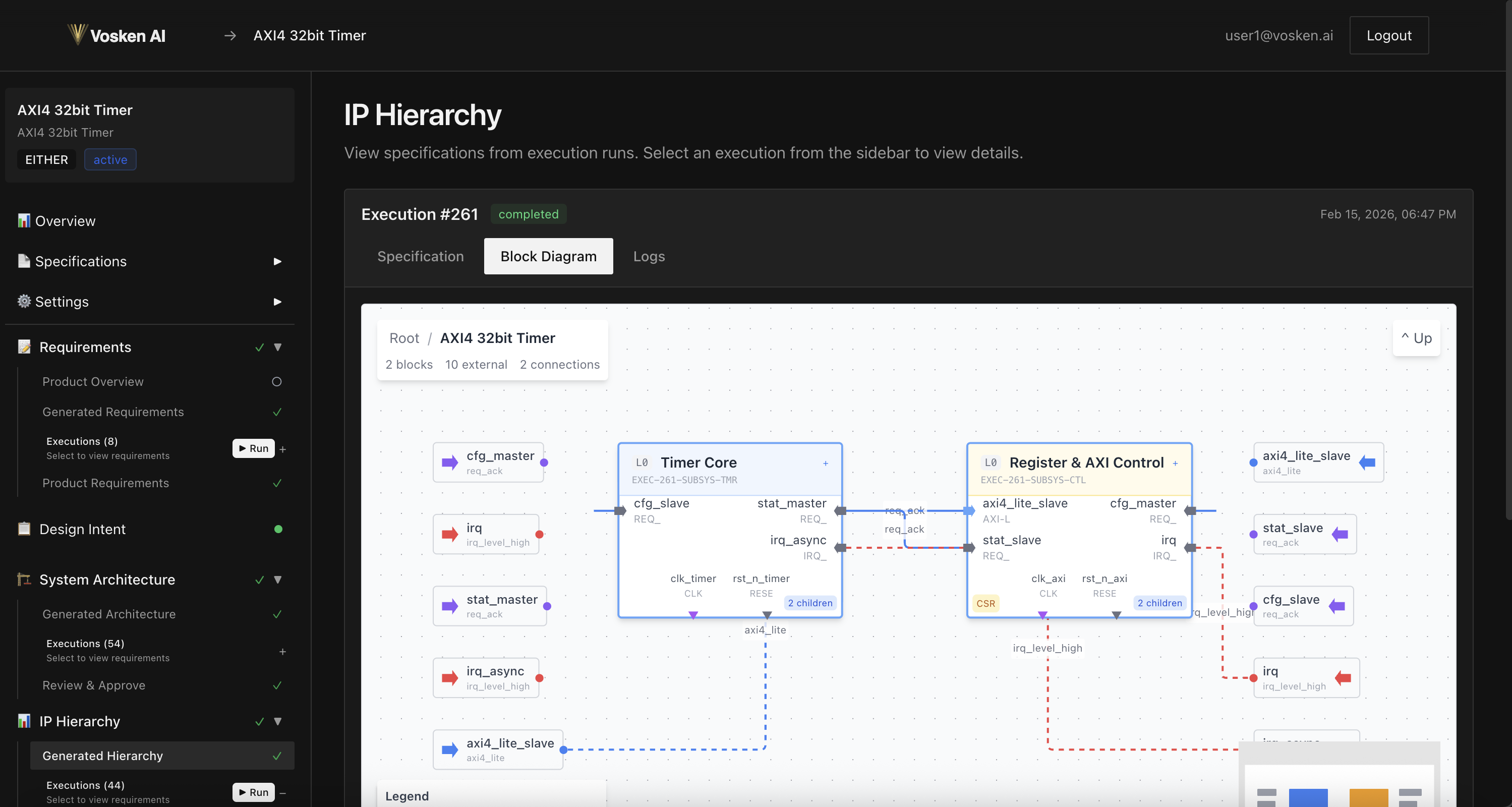

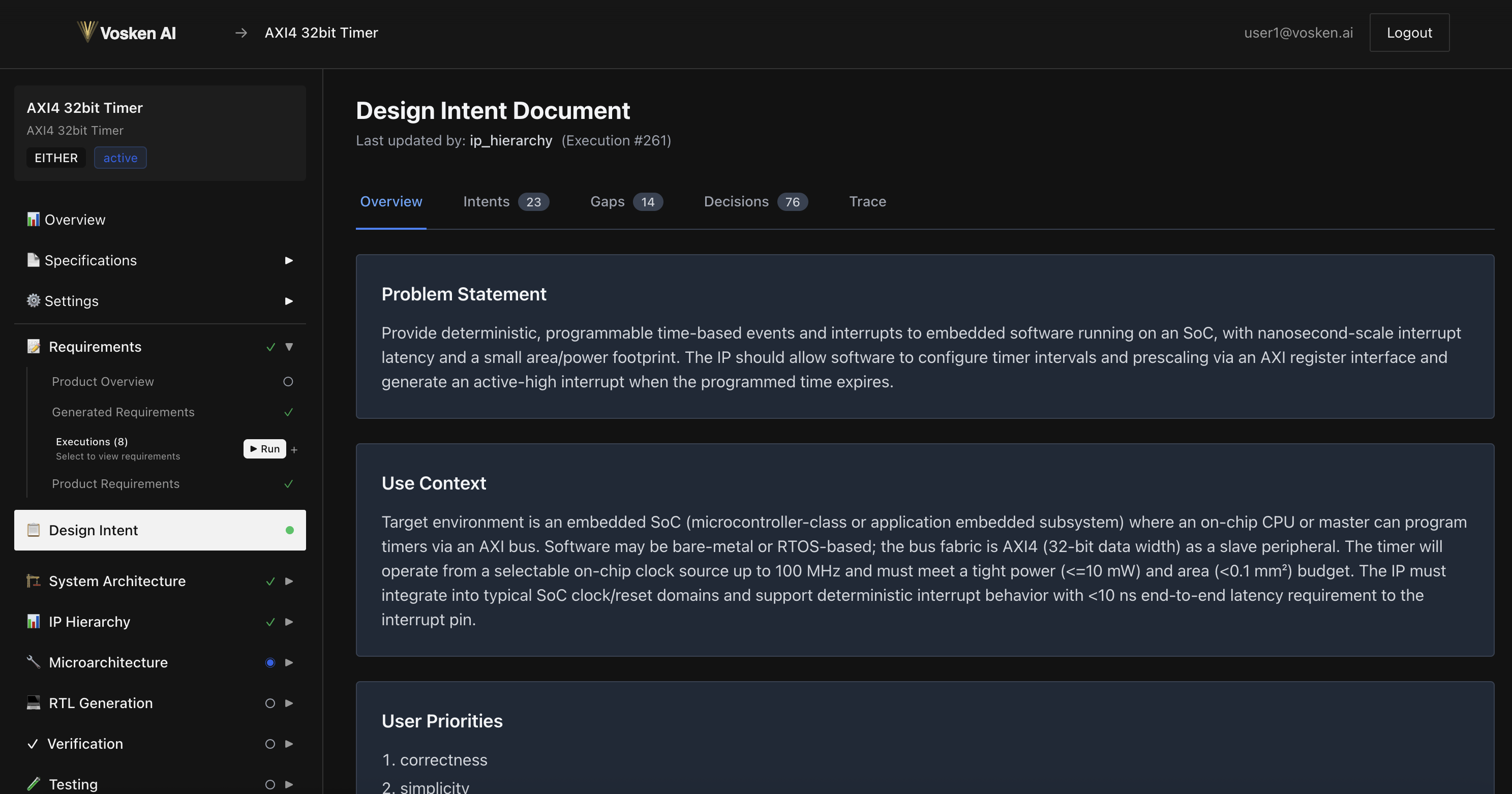

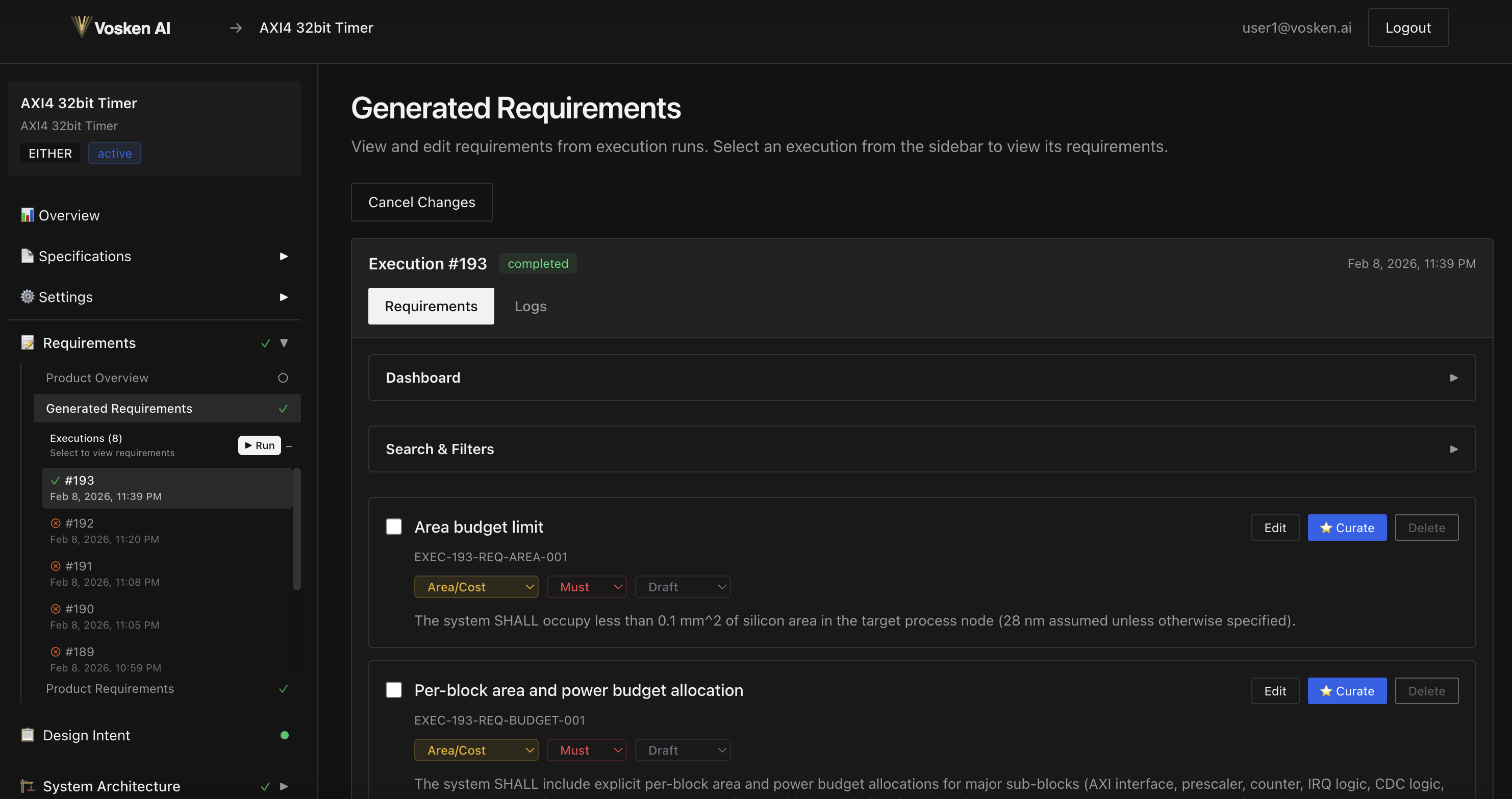

Real output from Vosken AI — an AXI4 32-bit Timer designed from a single product brief.

Built for chip design teams shipping on tight deadlines. ASIC, FPGA, or both.

The AI platform that automates the full chip design pipeline — from intent to verified silicon IP. Built for ASIC and FPGA teams shipping on tight deadlines.

Intent to verified IP

Not months

RTL + Verification + UVM

The Pipeline

Each stage is powered by specialised AI agents that generate, review, and refine — delivering production-quality output at every step.

Natural language briefs into structured, testable requirements

Subsystem decomposition with clock/reset domains and interconnects

Top-down IP decomposition with intelligent reuse

Ports, registers, state machines, CDC plans, timing constraints

IEEE 1666-compliant functional models for early validation

Lint-clean, synthesizable SystemVerilog with Verilator refinement

Test plans, coverage goals, and VIP selection

Complete UVM environment — agents, drivers, monitors, scoreboards

The Product

Real output from Vosken AI — an AXI4 32-bit Timer designed from a single product brief.

Built for chip design teams shipping on tight deadlines. ASIC, FPGA, or both.

Why Vosken

Your team stays in control. Our AI handles the rest — across the entire pipeline.

From intent to verified IP — every stage connected, every handoff automated, fully integrated.

Built on IEEE 1800, IEEE 1666, and UVM 1.2. Our AI understands hardware semantics — not just code patterns.

AI amplifies your team's expertise — handling the heavy lifting so engineers focus on what matters most.

Ship chips in weeks, not months. Production-quality output validated against industry standards from day one.

The Difference

Traditional Flow

5+ engineers, manual handoffs,

error-prone iterations

With Vosken AI

Your teams review, AI generates.

Arch, design, and verification — each team stays in the loop.

Your Workflow

A full-featured web interface for visual control, or a powerful CLI for engineers who live in the terminal.

Standards

Every output is validated against the standards your team already works with.

SystemVerilog

SystemC

IEEE 1800.2

AXI4 / APB / AHB

Open bus

Register design

Avionics

Automotive safety

Design Partners

We're accepting a limited number of design partners for our beta. Here's what you get.

Full platform access at no cost. Early partners lock in preferred pricing when we launch.

Weekly calls, shared Slack channel, and your feedback directly shapes the roadmap.

Your designs run first. Issues get fixed fast. You're not a ticket — you're a partner.

Join the engineers designing hardware at the speed of thought. We'll be in touch within 24 hours.

We'll be in touch within 24 hours. In the meantime, explore our full feature set.

Vosken AI is built by engineers with deep experience in ASIC/FPGA design, verification, and AI — based in the UK. We've lived the pain of manual RTL workflows and built the tool we wished existed.

Questions? [email protected]